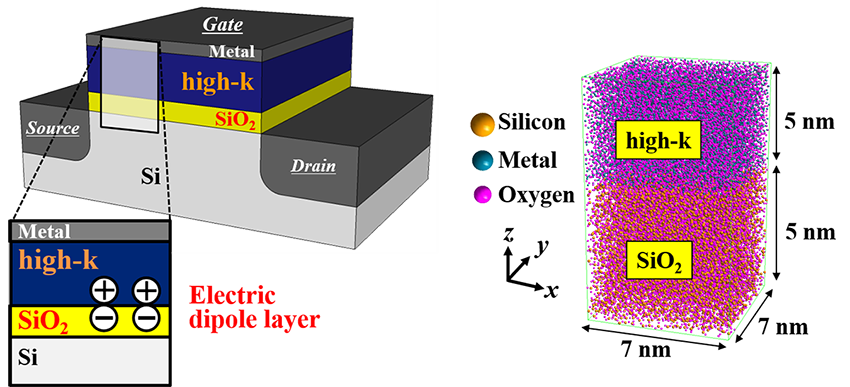

MOSFETに高誘電率(high-k)ゲート絶縁膜を導入すると、しきい値電圧のコントロールが難しくなります。これは、high-k絶縁膜と界面SiO2層の間に電気的ダイポール層が形成されるためと考えられています。当研究室では、このダイポール層の形成メカニズムを古典分子動力学(Molecular Dynamics; MD)シミュレーションを用いて調査しています。

![]()

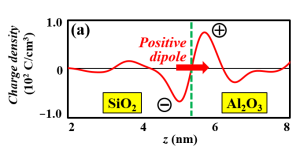

Al2O3/SiO2積層構造の場合、MOSFETのしきい値がプラスの方向にシフトすることが実験で明らかにされています。我々のMDシミュレーションでも、Al2O3側からSiO2側へと酸素イオンの移動が起こり、しきい値シフトの実験値を定量的に再現するダイポール層が自然に出現することがわかりました。

- Ryota Kunugi, Nobuhiro Nakagawa, Takanobu Watanabe, “Driving force of oxygen ion migration across high‐k/SiO2 interface,” Applied Physics Express, Vol. 10, 031501 (2017). doi:10.7567/APEX.10.031501

- Kosuke Shimura, Ryota Kunugi, Atsushi Ogura, Shinichi Satoh, Jiayang Fei, Koji Kita, Takanobu Watanabe, “Positive and Negative Dipole Layer Formation at High-k/SiO2 Interfaces Simulated by Classical Molecular Dynamics,” Japanese Journal of Applied Physics, Vol.55, 04EB03 (2016). doi:10.7567/JJAP.55.04EB03

- Ryo Kuriyama, Masahiro Hashiguchi, Ryusuke Takahashi, Atsushi Ogura, Shinichi Satoh, and Takanobu Watanabe, “Molecular Dynamics Study on the Formation of Dipole Layer at High-k/SiO2 Interfaces,” Japanese Journal of Applied Physics Vol. 53, 08LB02, (2014).doi:10.7567/JJAP.53.08LB02